Analytical threshold voltage and drain-induced barrier lowering models of elliptic junctionless Gate-All-Around FET

Author affiliations

DOI:

https://doi.org/10.15625/2525-2518/20573Keywords:

Elliptic, Gate-All-Around, Threshold voltage, DIBL, EccentricityAbstract

The analytical models have been presented to determine the threshold voltage and Drain-Induced Barrier Lowering (DIBL) of an elliptic junctionless Gate-All-Around (GAA) FET. Because it is difficult to fabricate a GAA FET with an accurate circular cross-section, an analysis of an elliptic GAA FET is required. The values obtained using the proposed analytical threshold voltage and DIBL models were confirmed to be in good agreement, compared to other papers that had already been verified. Using this analytical threshold voltage and DIBL models, the threshold voltage and DIBL were analyzed according to the eccentricity of the elliptic cross-section structure. As a result, it was found that the absolute value of the minimum central potential increases as eccentricity increases, thereby increasing the threshold voltage. Additionally, the absolute value of the minimum central potential decreases as the drain voltage increases, thereby decreasing the threshold voltage, and this decreasing rate, i.e. DIBL, reduces as eccentricity increases. Therefore, threshold voltage and DIBL showed a mutual trade-off relationship for eccentricity. The threshold voltage and DIBL showed little change when the eccentricity was less than about 0.75. However, the threshold voltage and DIBL showed a large change along with a decrease in the effective channel radius when it was more than 0.75.

Downloads

References

1. Jiao H., Wang X., Wu S., Chen Y., Chu J., Wang J. - Ferroelectric field effect transistor for electronics and optoelectronics. Applied Physics Reviews 10 (2023) 011310. DOI:10.1063/5.0090120

2. Raffel Y., Muller F., Thunder S., Sk M. R., Lederer M., Pirro L., Beyer S., Seidel K., Chakrabarti B., Kampfe T., De S. - 28 nm high-k-metal gate ferroelectric field effect transistors based synapses - A comprehensive overview. Memories - Materials, Devices, Circuits and Systems 4 (2023) 100048. DOI:10.1016/j.memori.2023.100048

3. Blessy P. H., Shenbagavalli A., Samuel T. S. A. - A Comprehensive Review on the Single Gate, Double Gate, Tri-Gate, and Heterojunction Tunnel FET for Future Generation Devices. Silicon 15 (2023) 2385-2405. DOI:10.1007/s12633-022-02189-2

4. Chen M., Sun X., Liu H., Wang H., Zhu Q., Wang S., Du H., Dong B., Zhang J., Sun Y., Qiu S., Alava T., Liu S., Sun D., Han Z. - A FinFET with one atomic layer channel. Nature Communication 11 (2020) 1205. DOI:10.1038/s41467-020-15096-0

5. Mukesh S., Zhang J. - A Review of the Gate-All-Around Nanosheet FET Process Opportunities. Electronics 11 (2022) 3589. DOI:10.3390/electronics11213589

6. Wong H., Kakushima K. - On the Vertically Stacked Gate-All-Around Nanosheet and Nanowire Transistor Scaling beyond the 5 nm Technology Node. Nanomaterials 12 (2022) 1739. DOI:10.3390/nano12101739

7. Mohapatra E., Dash T. P., Jena J., Das S., Maiti C. K. - Design study of gate-all-around vertically stacked nanosheet FETs for sub-7 nm nodes. SN Applied Sciences 3 (2021) 540. DOI:10.1007/s42452-021-04539-y

8. Zhang Z., Lin Z., Liao P., Askarpour V., Dou H., Shang Z., Xharnas A., Si M., Alajlouni S., Shakouri A., Wang H., Lundstrom M., Maassen J., Ye P. D. - A Gate-All-Around In2O3 Nanoribbon FET With Near 20 mA/um Drain Current. IEEE Electron Device Letters 43 (2022) 1905-1908. DOI:10.1109/LED.2022.3210005

9. Zhao F., Jia X., Luo H., Zhang J., Mao X., Li Y., Luo J., Wang W., Li Y. - Hybrid integrated Si nanosheet GAA-FET and Stacked SiGe/Si FinFET using selective channel release strategy. Microelectronic Engineering 275 (2023) 111993. DOI:10.1016/j.mee2023.111993

10. Hofman S. – What is a gate-all-around transistor?, https://asml.com/en/news/stories/2022/ what-is-a-gate-all-around-transistor (accessed 21 January 2024)

11. Chen Z. - Gate-all-around nanosheet transistors go 2D. Natureelectronics 5 (2022) 830-831. DOI:10.1038/s41928-022-00899-4

12. Qing Y., Chiang T., Wang L., Du F., Xie T., Cao Y., Liu Z. - Novel Omega-Gate heterojunction tunneling FET with a new analytical model. Semiconductor Science and Technology 36 (2021) 065011. DOI:10.1088/1361-6641/abf665

13. Karbalaei M., Dideban D., Heidari H. - A sectorial scheme of gate-all-around field effect transistor with improved electrical characteristics. Ain Shams Engineering Journal 12 (2021) 755-760. DOI:10.1016/j.asej.2020.04.015

14. Darwish T., Bayoumi M. - The Electrical Engineering Handbook. 5. Trends in Low-Power VLSI Design. ACADEMIC PRESS, New York (2005) 263-280. DOI:10.1016/B978-012170960-0/50022-0

15. Bangsaruntip S., Cohen G. M., Majumdar A., Sleight J. W. - Universality of Short-Channel Effects in Undoped-Body Silicon Nanowire MOSFETs. IEEE Electron Device Letters 31 (2010) 903-905. DOI:10.1109/LED.2010.2052231

16. Han J., Moon D., Choi Y. - High Aspect Ratio Silicon Nanowire for Stiction Immune Gate-All-Around MOSFETs. IEEE Electron Device Letters 30 (2009) 864-866. DOI:10.1109/LED.2009.2024178

17. Lee M., Park B., Cho I., Lee J. - Characteristics of Elliptical Gate-All-Around SONOS Nanowire Effective Circular Radius. IEEE Electron Device Letters 33 (2012) 1613-1615. DOI:10.1109/LED.2012.2215303

18. Chao P., Li Y. - Impact of Geometry Aspect Ratio on 10-nm Gate-All-Around Silicon-Germanium Nanowire Field Effect Transistors. Proceedings of 14th IEEE International Conference on Nanotechnology, IEEE (2014) 452-455. DOI:10.1109/NANO.2014.6968188

19. Jha S., Kumar A., Kumar S. - Impact of Elliptical Cross-Section on Some Electrical Properties of Gate-All-Around MOSFETs. Bonfring International Journal of Power Systems and Integrated Circuits 2 (2012) 18-22. DOI:10.9756/BIJPSIC.3139

20. Kumar S., Jha S. - Impact of elliptical cross-section on the propagation delay of multi-channel gate-all-around MOSFET based inverters. Microelectronics Journal 44 (2013) 844-851. DOI:10.1016/j.mejo.2013.06.003

21. Kumari A., Kumar S., Sharma T. K., Das M. K. - On the C-V characteristics of nanoscale strained gate-all-around Si/SiGe MOSFETs. Solid State Electronics 154 (2019) 36-42. DOI:10.1016/j.sse.2019.02.006

22. Zhang L., Li L., He J., Chan M. - Modeling Short-Channel Effect of Elliptical Gate-All-Around MOSFET by Effective Radius. IEEE Electron Device Letters 32 (2011) 1188-1190. DOI:10.1109/LED.2011.2159358

23. Chiang T. - Elliptical nanowire FET: Modeling the short-channel subthreshold current caused by interface-trapped-charge and its evaluation for subthreshold logic gate. Superlattices and Microstructures 149 (2021) 106751. DOI:10.1016/j.spmi.2020.106751

24. Kumar P., Koley K., Mech B. C., Maurya A., Kumar S. - Analog and RF performance optimization for gate all around tunnel FET using broken-gap material. Scientific Reports 12 (2022) 18254. DOI:10.1038/s41598-022-22485-6

25. Colinge J., Lee C., Afzalian A., Akhavan N. D., Yan R., Ferain I., O’nell B., Blake A., White M., Kelleher A., McCarthy B., Murphy R. - Nanowire transistors without junctions. Nature Nanotechnology 5 (2010) 225-229. DOI:10.1038/nnano.2010.15

26. Nowbahari A., Roy A., Marchetti L. - Junctionless Transistors: State-of-the-Art. Electronics 9 (2020) 1174. DOI: 10.3390/electronics9071174

27. Hu G., Xiang P., Ding Z., Liu R., Wang L., Tang T. - Analytical Models for Electric Potential, Threshold Voltage, and Subthreshold Swing of Junctionless Surrounding-Gate Transistors. IEEE Trans. on Electron Devices, 61 (2014) 688-695. DOI:10.1109/TED.2013.2297378

28. Kumar A., Pattanaik M., Srivastava P., Jha K. K. - Reduction of Drain Induced Barrier Lowering in DM-HD-NA GAAFET for RF Applications. IET Circuits, Devices & Systems 14 (2020) 270-275. DOI:10.1049/iet-cds.2019.0306

29. Yu T., Lu W., Zhao Z., Si P., Zhang K. - Negative drain-induced barrier lowering and negative differential resistance effects in negative-capacitance transistors. Microelectronics Journal 108 (2021) 104981. DOI:10.1016/j.mejo.2020.104981

30. Jung H. K. - SPICE Model of Drain Induced Barrier Lowering in Junctionless Cylindrical Surrounding Gate (JLCSG) MOSFET. J. Korean Inst. Electr. Electron. Mater. Eng. 31 (2018) 278-282. DOI:10.4313/JKEM.2018.31.5.278

31. Dimitrijev S. - Principles of Semiconductor Devices, 2nd. Oxford, New York (2012).

32. Jung H. K. - SPICE model of drain induced barrier lowering in sub-10 nm junctionless cylindrical surrounding gate MOSFET. International Journal of Electrical and Computer Engineering 10 (2020) 1288-1295. DOI:10.11591/ijece.v10i2.pp1288-1295.

Downloads

Published

How to Cite

Issue

Section

License

This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.

Vietnam Journal of Sciences and Technology (VJST) is an open access and peer-reviewed journal. All academic publications could be made free to read and downloaded for everyone. In addition, articles are published under term of the Creative Commons Attribution-ShareAlike 4.0 International (CC BY-SA) Licence which permits use, distribution and reproduction in any medium, provided the original work is properly cited & ShareAlike terms followed.

Copyright on any research article published in VJST is retained by the respective author(s), without restrictions. Authors grant VAST Journals System a license to publish the article and identify itself as the original publisher. Upon author(s) by giving permission to VJST either via VJST journal portal or other channel to publish their research work in VJST agrees to all the terms and conditions of https://creativecommons.org/licenses/by-sa/4.0/ License and terms & condition set by VJST.

Authors have the responsibility of to secure all necessary copyright permissions for the use of 3rd-party materials in their manuscript.

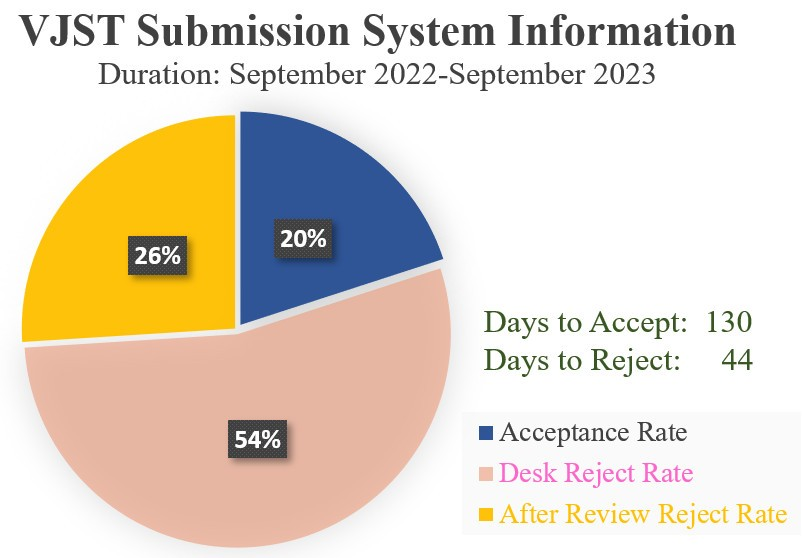

Vietnam Journal of Science and Technology (VJST) is pleased to notice:

Vietnam Journal of Science and Technology (VJST) is pleased to notice: